|

|

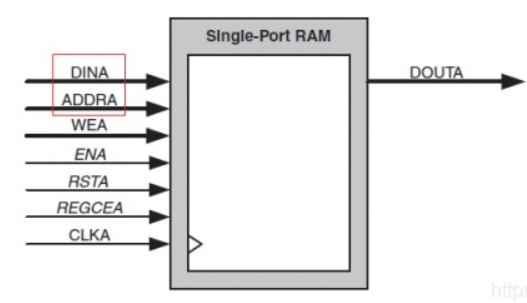

一、单端口RAM

单端口 RAM 指的是只有一个读写口,就是只有一组数据线和地址线,就是读和写都是通过这个口来访问 RAM,但是同一个时刻只能访问一个,要么是读,要么是写。

单端口sram电路图

单端口sram信号

RAM 模型主要有一个二维的 RAM 存储,写入数据处理和读出数据处理,读出数据在读使能无效时,输出“X”态,那么为什么输出“X”态呢,输出“X”态是为了避免使用无效的读数据,防止逻辑使用错误。RAM 读无效时的数据我们不建议使用,我们一般只使用 RAM 读有效时的RAM 读数据。

module sp_ram (

input clock , //ram clk

input wen , //ram 写使能 WEN

input en , //ram 总使能 ENA

input [4:0] address , //ram 读写地址 ADDA

input [7:0] data , //ram 写数据 DINA

output reg [7:0] q //ram 读数据 DOUTA

);

//reg define

reg [7:0] ram [15:0] ; //ram 数据

//*****************************************************

//** main code

//*****************************************************

always @(posedge clock ) begin

if(wen && en)

ram[address] <= data;

end

always @(posedge clock ) begin

if(( wen == 1&#39;b0) && en)

q <= ram[address];

else

q <= 8&#39;hx ;

end

endmodule

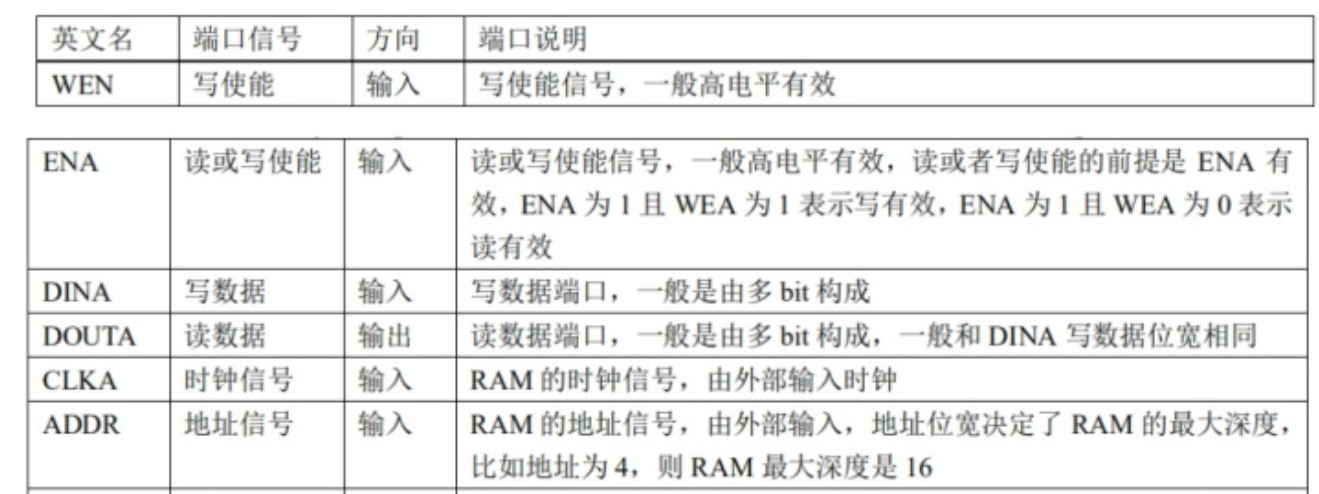

二、伪双端口RAM

伪双端口 RAM 指的是有两个读写端口,但是一个端口只能读,一个端口只能写,伪双端口 RAM 一般叫 TP RAM。一般 FIFO 内部例化的都是伪双端口 RAM。

下面我们来看下伪双端口 RAM,伪双端口 RAM 指的是有两个读写口,就是有两组数据线和地址线,一组是写数据线,一组是读数据线,同一个时刻写和读可以同时访问。

伪双端口sram电路图

伪双端口sram信号

RAM 模型主要有一个二维的 RAM 存储,写入数据处理和读出数据处理,读出数据在读使能无效时,输出“X”态,那么为什么输出“X”态呢,输出“X”态是为了避免使用无效的读数据,防止逻辑使用错误。RAM 读无效时的数据我们不建议使用,我们一般只使用 RAM 读有效时的 RAM 读数据。

module tp_ram (

input clocka , //ram clk

input clockb , //ram clk

input wea, //ram A端口写使能 WEA

input ena, //ram A端口使能 ENA

input enb, //ram B端口使能 ENB

input [4:0] wr_address , //ram 写地址 ADDA

input [4:0] rd_address , //ram 写地址 ADDB

input [7:0] data , //ram 写数据 DINA

output reg [7:0] q //ram 读数据 DOUTB

);

//reg define

reg [7:0] ram [31:0] ; //ram 数据

//*****************************************************

//** main code

//*****************************************************

always @(posedge clocka ) begin

if(ena & wea)

ram[wr_address] <= data;

end

always @(posedge clockb ) begin

if(enb)

q <= ram[rd_address];

else

q <= 8&#39;hx ;

end

endmodule

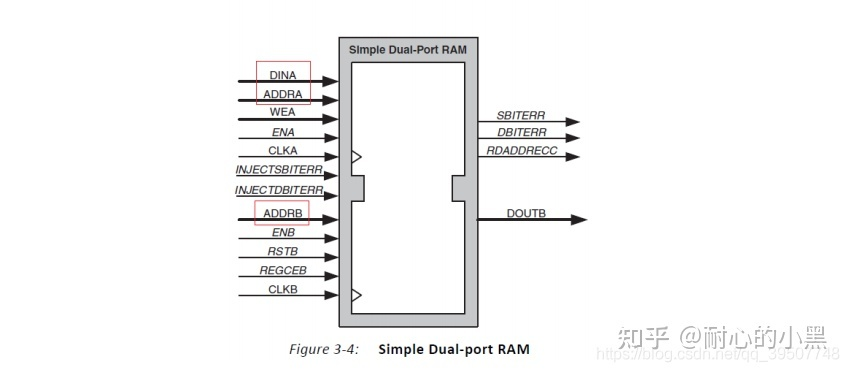

三、真双端口RAM

真双端口 RAM 指的是有两个读写端口,每个端口都可以独立发起读或者写。下面我们来看下真双端口 RAM,真双端口 RAM 指的是有两个独立的读写口,就是有两组数据线和地址线,一组是读或者写数据线,另外一组也是读或者写数据线,同一个时刻两个端口可以同时访问,两个端口可以是读和读,也可以是写和读,还可以是写和写。

真双端sram电路图

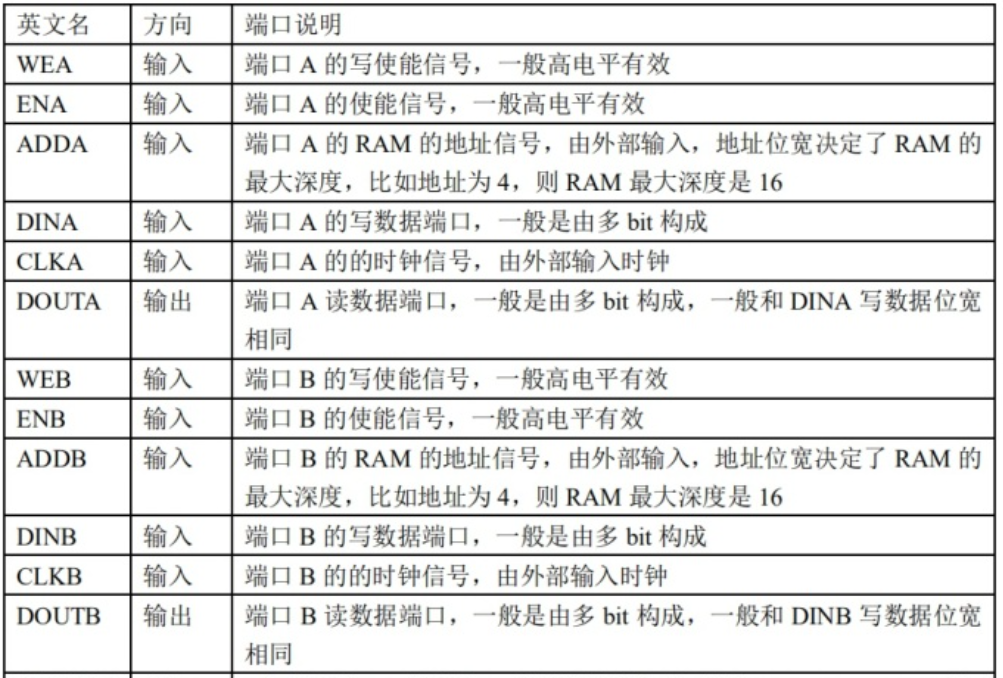

真双端口信号

module dp_ram (

input clocka , //ram clk

input clockb , //ram clk

input ena, //ram A端口使能 ENA

input enb, //ram B端口使能 ENB

input wea, //ram 写使能 WEA

input web, //ram 写使能 WEB

input [4:0] address_a , //ram 写地址

input [4:0] address_b , //ram 写地址

input [7:0] data_a , //ram 写数据 DINA

input [7:0] data_b , //ram 写数据 DINB

output reg [7:0] q_a , //ram 读数据 DOUTA

output reg [7:0] q_b //ram 读数据 DOUTB

);

//reg define

reg [7:0] ram [31:0] ; //ram 数据

//*****************************************************

//** main code

//*****************************************************

always @(posedge clocka ) begin

if(ena & wea)

ram[address_a] <= data_a;

end

always @(posedge clockb ) begin

if(enb & web)

ram[address_b] <= data_b;

end

always @(posedge clocka ) begin

if(ena & !wea)

q_a <= ram[address_a];

else

q_a <= 8&#39;hx ;

end

always @(posedge clockb ) begin

if(enb & !web)

q_b <= ram[address_b];

else

q_b <= 8&#39;hx ;

end

endmodule

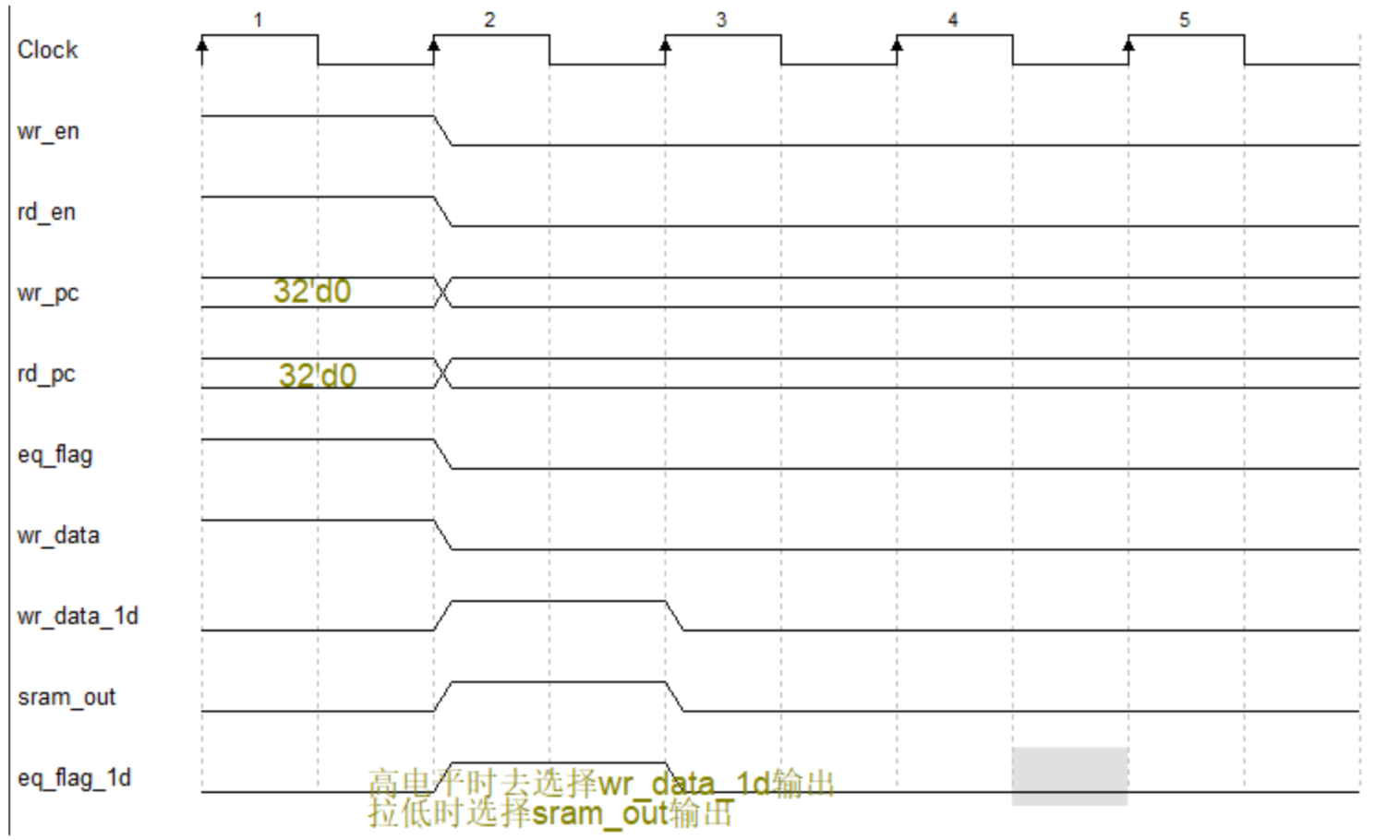

四、当读写地址相同时

双端口同时读写冲突问题:

考虑到当双口sram同时对同一个地址进行读写时,会产生冲突

解决办法(采用读出的数据是刚刚将要往里写的数据的方式):

定义一个flag,由wr_en && rd_en && (wr_addr == rd_addr)构成

1.当flag为高电平时,将写数据打一拍记为wr_data_1d

2.将flag打一拍作为输出选择信号flag_1d

3.用flag_1d信号去选择输出数据 out = flag_1d ? wr_data_1d :sram_data_out(sram的输出数据);

时序图:

伪双端口解决sram地址冲突时序图

摘自:手写RAM(单端口、伪双端口、真双端口) |

|